(2)视频信号处理(SXD3142R)

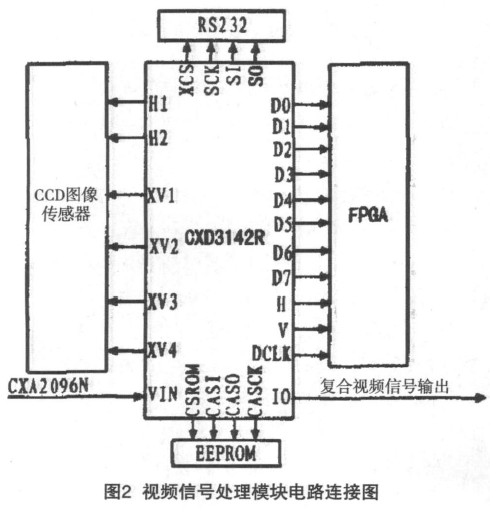

本设计采用SONY公司专用信号处理器件CXD3142作为信号处理器。CXD3142R是专用于对Ye,Cy,Mg和G补色单片CCD输出信号进行处理的低功耗、高效率的信号处理器:具有自动曝光和自动向平衡功能。可同时输出复合视频信号和YUV8位数字信号输出。内部集成9位A/D转换器同步信号产生电路、外部同步电路和时钟控制电路。此外,CXD3142R还具有串口通信功能。用户可在PC机中预先设定好DSP中的寄存器值,通过串口下载到DSP,并对图像信号进行自动曝光和自动白平衡等处理。图2为视频信号处理模块电路连接图。

图2中,Hl,H2,XVl,XV2,XV3。XV4是CCD图像传感器的时序驱动信号,EEPROM用来存储DSP初始化的寄存器值。DO~D7是YUV数字信号。其具体工作流程:将CCD图像传感器采集的模拟信号经CXA2096N进行相关预处理后。相应数字信号经VIN引脚传给DSP(CXD3142),DSP接收数字信号后,利用其内部AE/AWB检测电路、同步信号产生电路、外同步电路以及相关算法对其进行相关处理。处理完成后在行(H引脚)、场(V引脚)信号及时钟信号(PCLK)的控制下将8位数字信号经过D0~D7引脚传给FPGA模块进行相关处理。通过引脚SCK、SI、SO、XCS串口通信。通过CSROM、CASI、CSASO、CASCK引脚与外部EEPROM通信,实现DSP相关的初始化。此外。IO引脚输出经DSP处理过的复合视频信号,通过相关接口直接在CRT显示器上显示图像处理结果。

(3)FPGA模块

为了实现实时预处理数字视频信号数据,增加系统扩展性。该系统设计扩展一片由Xilinx公司生产的基于90am工艺制造的Spartan3E系列FPGA,其型号为XC3S250E-PQ208.4Cm,此FPGA具有较高的性价比,其内有25万个系统门,5508个逻辑单元(LC),612个可配置逻辑块(CLB),216Kbit的块RAM.12个专用乘法器,158个可用的I/O接口。4个数字时钟管理单元(DCM)。图3为其电路连接图。

DSP与FPGA的通信是由ll根总线完成的。分别是8根数据线,行、场同步信号和数据时钟总线。因为CXD3142RDSP输出PAL(逐行倒相)制式的数字视频信号。FPGA将此PAL制视频信号转换成VGA格式。首先将YUV(4∶2∶2)格式信号转换成RGB(5∶6∶5)格式,然后利用2个SDRAM作为帧缓存,利用场插值算法,完成隔行到逐行的转换,并将帧率由25Hz提升到60Hz,同时产生SVGA格式、帧频为60Hz的行、场同步信号。并把被放大的图像数据经D/A转换后输出列VGA接口,VGA显示器上实时显示采集的图像。

微信扫描二维码,关注公众号。